本次设计采用FPGA与D/A转换器完成四种波形的产生:递增斜波;递减斜波;三角波;递增阶梯波。

D/A转换器的功能是把二进制数字量电信号转换为与其数值成正比的模拟量电信号。在D/A参数中一个最重要的参数就是分辨率,它是指输入数字量发生单位数码变化时,所对应输出模拟量(电压或电流)的变化量。

本次以FPGA芯片EP3C10E144C8与廉价的并行8位D/A转换芯片AD558完成设计。

AD558芯片

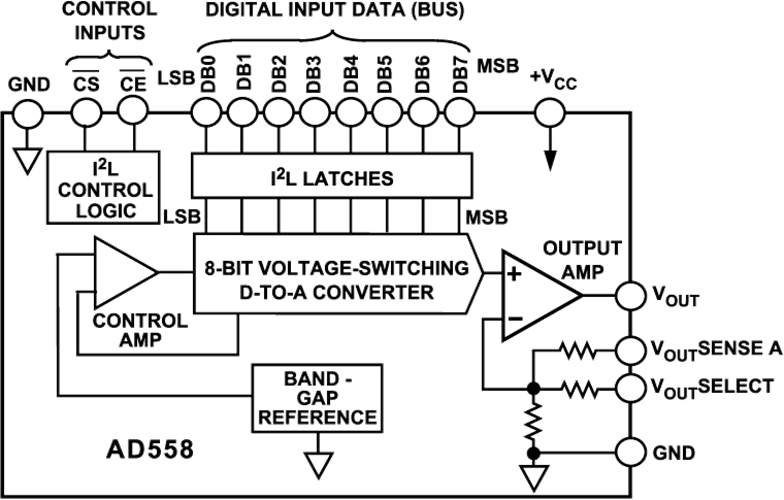

功能框图

可看出AD558由四个主要的功能块(控制逻辑、锁存器、DAC、能隙参考)固化在一个集成块上,而且内部有高速输出缓冲放大器、接换电阻与调节电阻,所以接口特别简单,且使用时无须外部调整即可获得±1/2LSB精度的电压。在该模块的锁存器和控制逻辑部分应用了低功率、小体积、高速度的IPL设计(IPL是一个完全兼容的线性双极性低功率的功能块结构)。这便使模块具有体积小、功耗低、速度快等特点。

主要性能

- 单电源供电(+5V~+15V)

- 完全8位D/A转换

- 内部标准能隙参考

- 完全兼容的微处理接口

- 无须外部电路补偿

- 建立时间快:

1μs - 功耗:

75mW - 低价格

- 封装:DIP16和PLCC20

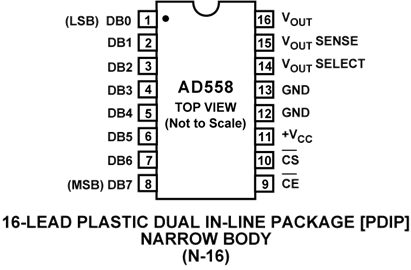

引脚图和引脚名称

| 引脚 | 符号 | 功能 |

|---|---|---|

| 1~8 | DB0~DB7 | 数字量输入 |

| 9 | CE/ | 使能端,CE/与CS/同时为低电平,选中芯片。 |

| 10 | CS/ | 片选端,和9脚共同决定是否选择芯片。 |

| 11 | +VCC | 为供电电源(+5V~+15V) |

| 12、13 | GND | 接地端 |

| 14、15 | VoutSENSE、VoutSELECT | 输出电压选择端(0~2.56v)或(0~10V) |

| 16 | Vout | 模拟电压输出端 |

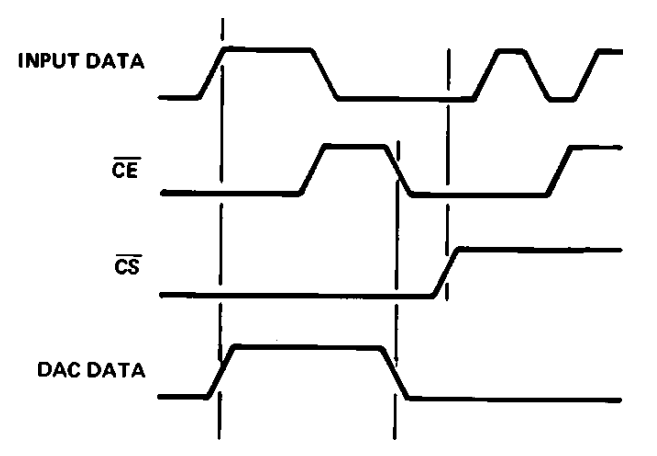

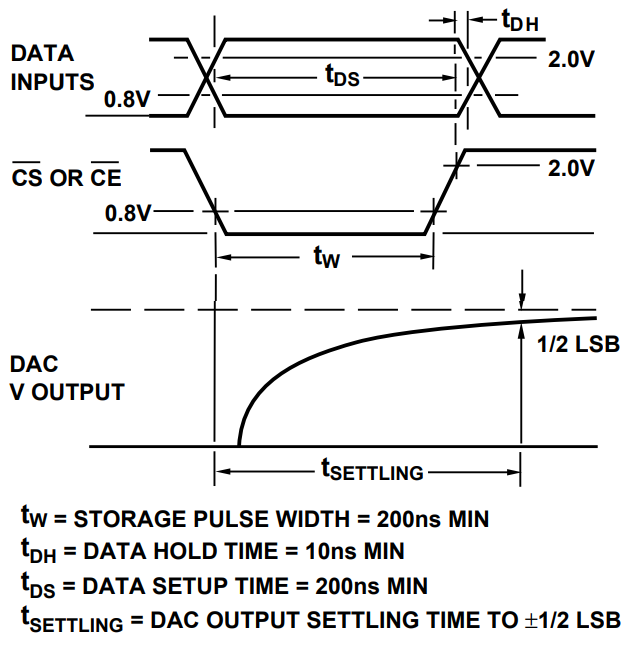

控制时序

可以看出,当CE/和CS/有一个为'1'时,锁存器工作,锁存输入的信号。直到CE/和CS/全为'0',开始下一个数据的转换。

因为我们的转换结果是实时输出的,所以只需将CE/和 CS/同时置为'0'就可以完成了。

verilog实现

递增斜波模块

对于输出是递增斜波,我们可采用0~255循环加法计数器实现。

module juchibo_ad(

input clk,

input rst_n,

output reg[7:0]daout

);

reg [7:0] tmp;

always @(posedge clk or negedge rst_n)begin

if (!rst_n)

tmp<=8'b0000_0000;

else if(tmp==8'b1111_1111)

tmp<=8'b0000_0000;

else

tmp<=tmp+1'b1;

daout<=tmp;

end

endmodule递减斜波模块

对于输出是递减斜波,我们可采用255~0循环减法计数器实现。

module juchibo_re(

input clk,

input rst_n,

output reg[7:0]daout

);

reg [7:0] tmp;

always @(posedge clk or negedge rst_n)begin

if (!rst_n)

tmp<=8'b1111_1111;

else if(tmp==8'b0000_0000)

tmp<=8'b1111_1111;

else

tmp<=tmp-1'b1;

daout<=tmp;

end

endmodule三角波模块

对于输出是三角波,我们可采用0~255~0循环加/减法计数器实现。

module sanjiaobo(

input clk,

input rst_n,

output reg[7:0]daout

);

reg [7:0] tmp;

reg flag;

always @(posedge clk or negedge rst_n)begin

if (!rst_n)begin

tmp<=8'b0000_0000;

flag<=0;

end

else if(flag==0)begin

if(tmp==8'b1111_1110)begin

tmp<=8'b1111_1111;

flag<=1;

end

else

tmp<=tmp+1'b1;

end

else begin

if(tmp==8'b0000_0001)begin

tmp<=8'b0000_0000;

flag<=0;

end

else

tmp<=tmp-1'b1;

end

daout<=tmp;

end

endmodule阶梯波模块

对于输出是递增阶梯波,我们可采用00H、20H、40H、60H、80H、A0H、C0H、E0H不同进制计数器实现。

module jiebo(

input clk,

input rst_n,

output reg[7:0]daout

);

reg [3:0] sum;

always @(posedge clk or negedge rst_n)begin

if (!rst_n)

sum<=4'd0;

else if(sum==4'd7)

sum<=4'd0;

else

sum<=sum+1;

case(sum)

4'd0: daout<=8'h00;

4'd1: daout<=8'h20;

4'd2: daout<=8'h40;

4'd3: daout<=8'h60;

4'd4: daout<=8'h80;

4'd5: daout<=8'ha0;

4'd6: daout<=8'hc0;

4'd7: daout<=8'he0;

default: daout<=8'h00;

endcase

end

endmodule控制模块

这里输入的en,对应两位拨码开关。其状态00~11对应四种波形输出。

module control(

input clk,

input [1:0] en,

input [7:0] juchibo_ad,

input [7:0] juchibo_re,

input [7:0] sanjiaobo,

input [7:0] jiebo,

output reg[7:0] daout

);

always @(posedge clk)begin

case(en)

2'b00: daout<=juchibo_ad;

2'b01: daout<=juchibo_re;

2'b10: daout<=sanjiaobo;

2'b11: daout<=jiebo;

default: daout<=juchibo_ad;

endcase

end

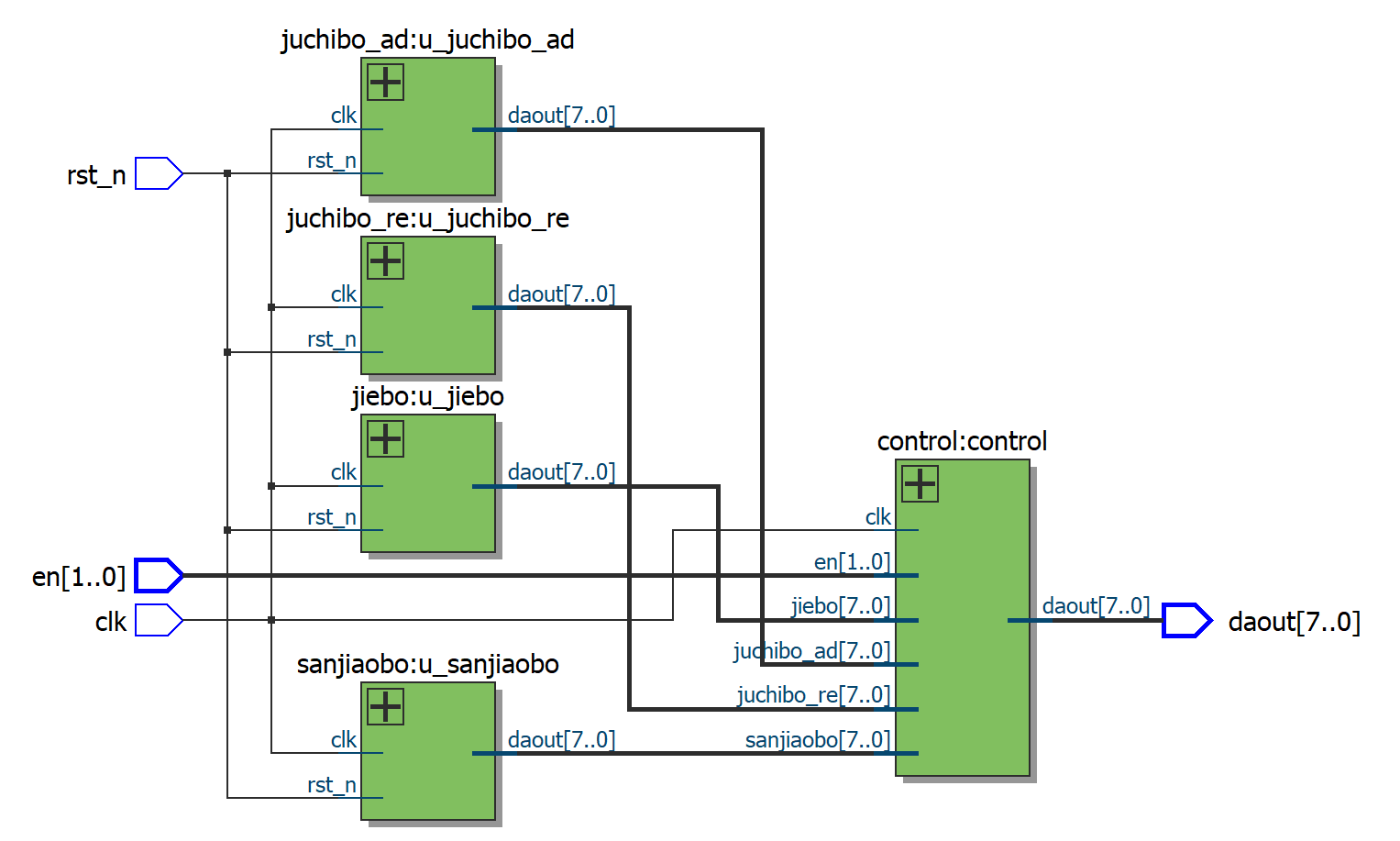

endmodule顶层文件

例化,综合。就是将各个模块连接起来就行了。

module main(

input clk,

input rst_n,

input [1:0]en,

output [7:0]daout

);

wire [7:0] juchibo_ad;

wire [7:0] juchibo_re;

wire [7:0] sanjiaobo;

wire [7:0] jiebo;

juchibo_ad u_juchibo_ad(

.clk (clk),

.rst_n (rst_n),

.daout (juchibo_ad)

);

juchibo_re u_juchibo_re(

.clk (clk),

.rst_n (rst_n),

.daout (juchibo_re)

);

sanjiaobo u_sanjiaobo(

.clk (clk),

.rst_n (rst_n),

.daout (sanjiaobo)

);

jiebo u_jiebo(

.clk (clk),

.rst_n (rst_n),

.daout (jiebo)

);

control control(

.clk (clk),

.en (en),

.juchibo_ad (juchibo_ad),

.juchibo_re (juchibo_re),

.sanjiaobo (sanjiaobo),

.jiebo (jiebo),

.daout (daout)

);

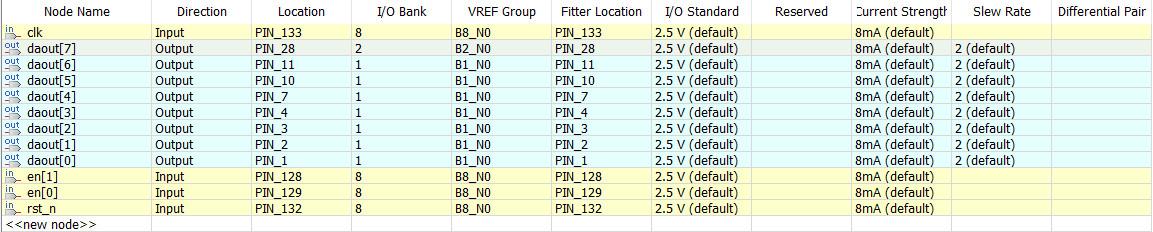

endmoduleEP3C10E144C8管脚配置

Quartus II里RTL原理图

验证

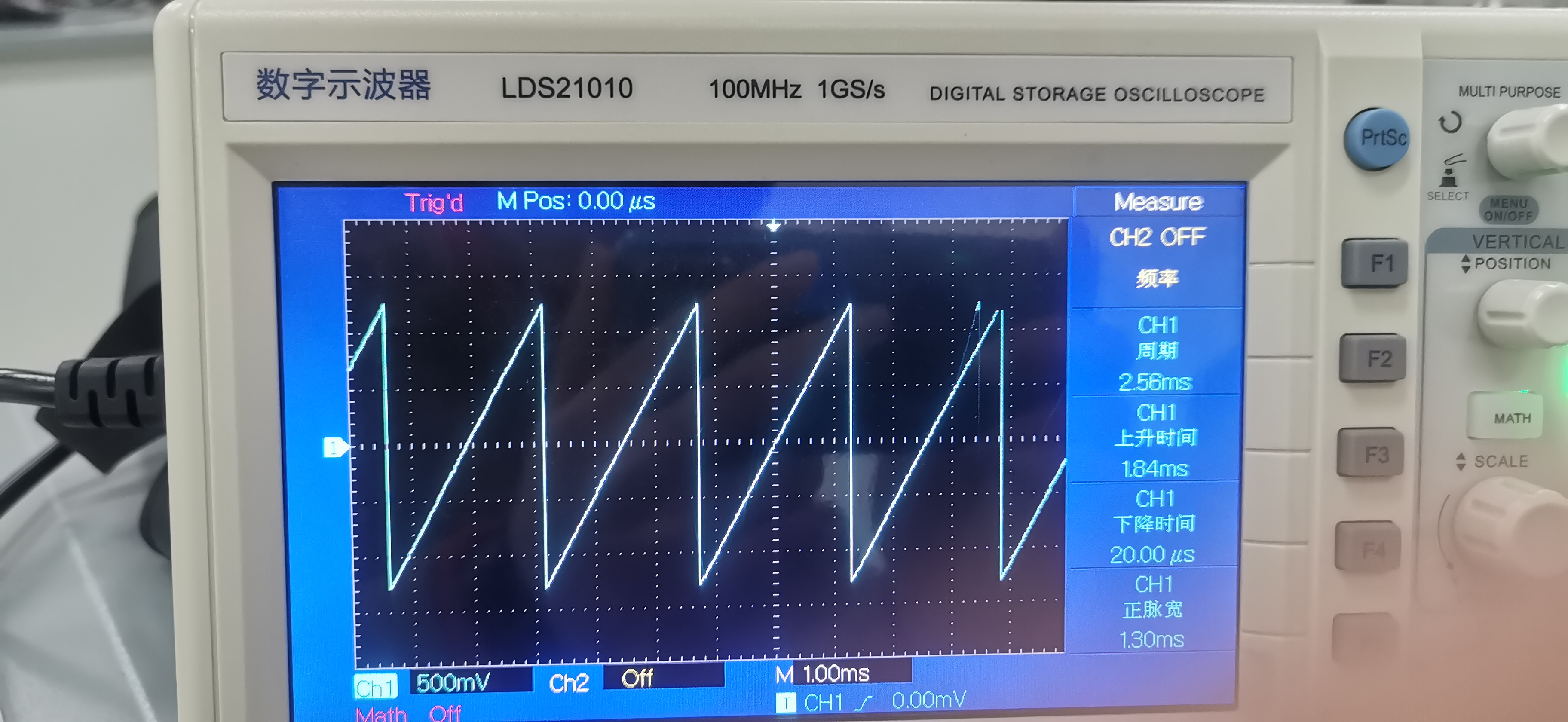

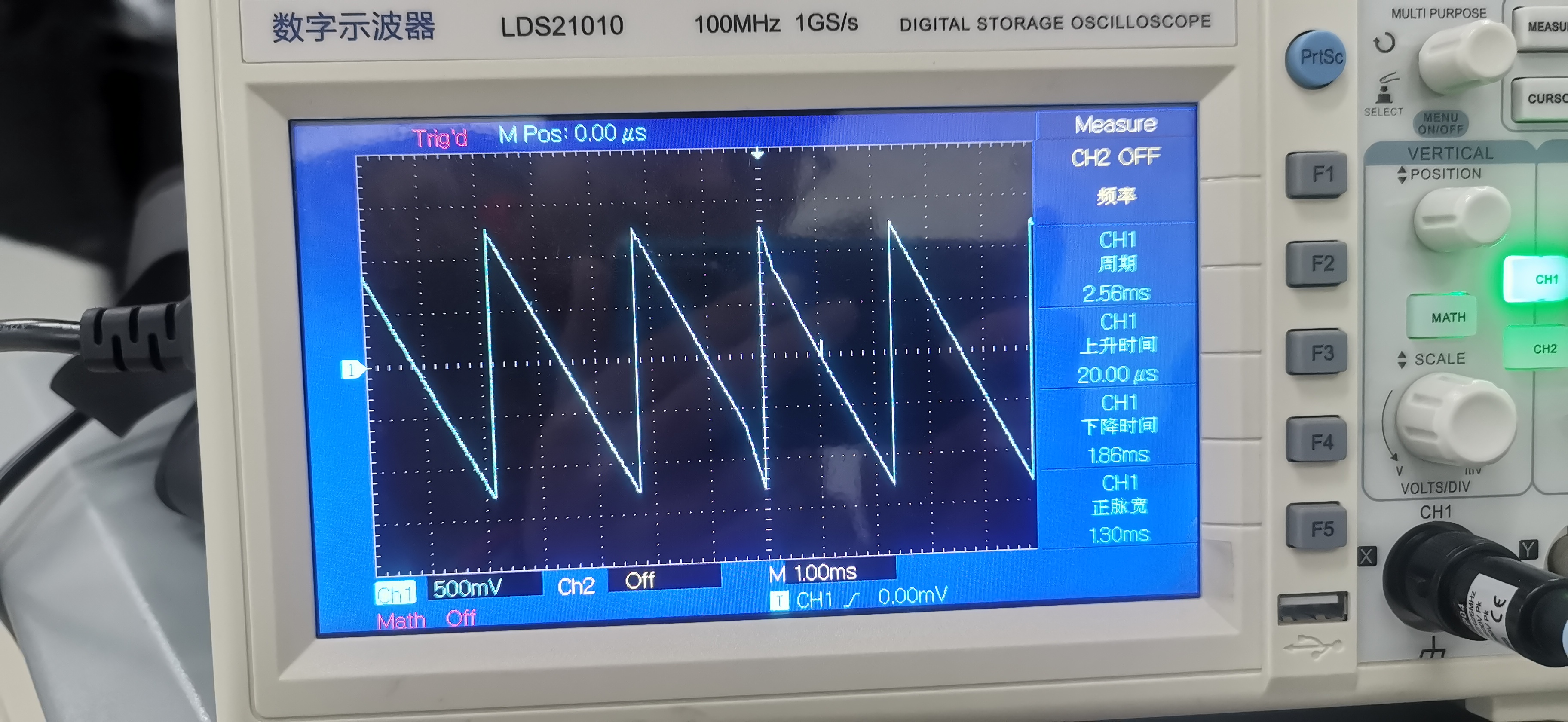

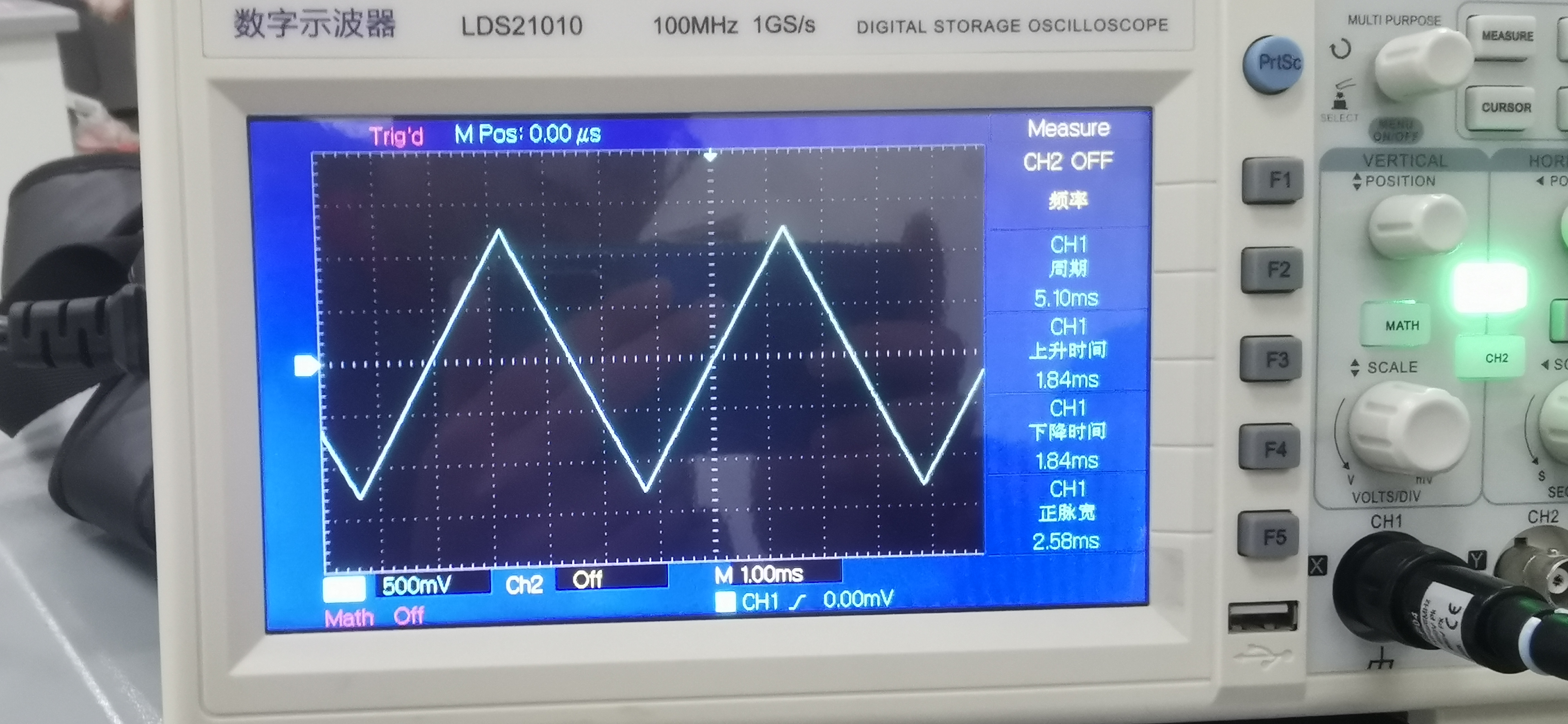

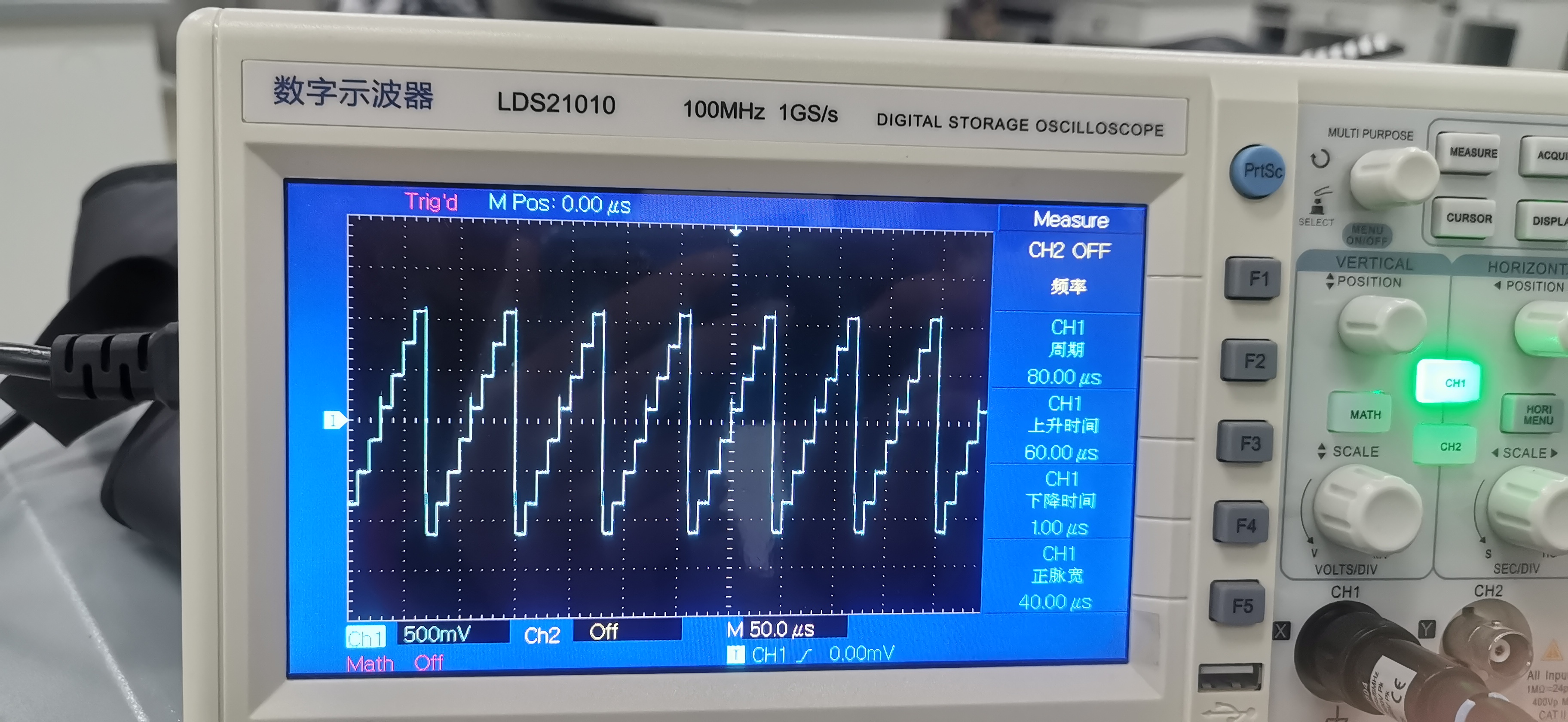

进行相关连线后,下载程序。通过示波器观察,可以看出:

拨码开关处于0,0时输出递增斜波

拨码开关处于0,1时输出递减斜波

拨码开关处于1,0时输出三角波

拨码开关处于1,1时输出阶梯波

9 条评论

呼和浩特洗浴荤素一览表a0gy.cn

寻找华纳圣淘沙公司开户代理(183-8890-9465薇-STS5099】

华纳圣淘沙官方合作开户渠道(183-8890-9465薇-STS5099】

华纳圣淘沙公司开户代理服务(183-8890-9465薇-STS5099】

华纳圣淘沙公司开户咨询热线(183-8890-9465薇-STS5099】

联系客服了解华纳圣淘沙开户

(183-8890-9465薇-STS5099】

华纳圣淘沙公司开户专属顾问

(183-8890-9465薇-STS5099】

华纳圣淘沙公司开户新手教程

零基础学会(183-8890-9465薇-STS5099)

华纳圣淘沙公司开户

华纳圣淘沙公司开户保姆级教程(183-8890-9465薇-STS5099)

一步步教你开通华纳圣淘沙公司账户(183-8890-9465薇-STS5099)

华纳圣淘沙公司开户分步图解

首次开户必看:(183-8890-9465薇-STS5099)

华纳圣淘沙全攻略

华纳圣淘沙公司开户实操手册(183-8890-9465薇-STS5099)

华纳圣淘沙开户流程视频教程

手把手教学:(183-8890-9465薇-STS5099)

华纳圣淘沙公司开户

华纳圣淘沙公司开户完全指南(183-8890-9465薇-STS5099)

华纳圣淘沙开户步骤详解(183-8890-9465—?薇-STS5099【6011643】

华纳圣淘沙公司开户流程全解析(183-8890-9465—?薇-STS5099【6011643】

华纳圣淘沙公司账户注册指南(183-8890-9465—?薇-STS5099【6011643】

新手如何开通华纳圣淘沙公司账户(183-8890-9465—?薇-STS5099【6011643】

华纳圣淘沙企业开户标准流程(183-8890-9465—?薇-STS5099【6011643】

华纳圣淘沙公司开户:从零到一(183-8890-9465—?薇-STS5099【6011643】

官方指南:华纳圣淘沙公司开户流程(183-8890-9465—?薇-STS5099【6011643】

华纳圣淘沙公司开户流程说明书(183-8890-9465—?薇-STS5099【6011643】

新盛客服电话是多少?(?183-8890-9465—《?薇-STS5099】【

新盛开户专线联系方式?(?183-8890--9465—《?薇-STS5099】【?扣6011643??】

新盛客服开户电话全攻略,让娱乐更顺畅!(?183-8890--9465—《?薇-STS5099】客服开户流程,华纳新盛客服开户流程图(?183-8890--9465—《?薇-STS5099】

案例丰富且贴合主题,论证逻辑环环相扣。

立意高远,以小见大,引发读者对社会/人性的深层共鸣。

社会责任感贯穿全文,彰显学者担当。

哈哈哈,写的太好了https://www.lawjida.com/